# M62486R

## VERY FAST CMOS 32K x 9 CACHE BRAM

#### ADVANCE DATA

- 32K x 9 CMOS SYNCHRONOUS BURST SRAM

- FAST CYCLE TIME 15ns

- FAST ACCESS TIMES: 8, 9ns Max

- ON-BOARD BURST COUNTER

- INPUT REGISTERS (ADDR., DATA, CTRL)

- SELF-TIMED WRITE CYCLE

- THREE STATE COMMON I/O

- HIGH OUTPUT DRIVE CAPABILITY

- ASYNCHRONOUS OUTPUT ENABLE (G)

- BURST CONTROL INPUTS: ADSP, ADSC, ADV

- DUAL CHIP SELECTS for EASY DEPTH EXPANSION

- OUTPUT REGISTERS for PIPE-LINE READ BURSTS

#### DESCRIPTION

The M62486R BRAM™ is a 288K (294,912 bit) CMOS Burst SRAM, organized as 32,768 words x

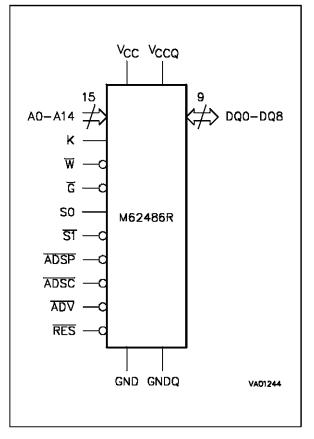

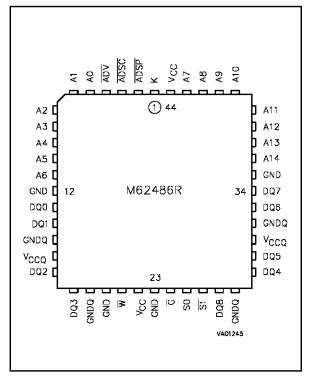

#### Table 1. Signal Names

| A0 - A14         | Address Inputs                  |

|------------------|---------------------------------|

| DQ0 - DQ8        | Data Inputs / Outputs           |

| К                | Clock                           |

| $\overline{W}$   | Write Enable                    |

| G                | Output Enable                   |

| S0               | Chip Select 0, Active High      |

| <u>S1</u>        | Chip Select 1, Active Low       |

| ADSP             | Address Status Processor        |

| ADSC             | Address Status Cache Controller |

| ADV              | Burst Address Advance           |

| Vcc              | Supply Voltage                  |

| GND              | Ground                          |

| V <sub>CCQ</sub> | Supply Voltage (DQ)             |

| GNDQ             | Ground (DQ)                     |

#### Figure 1. Logic Diagram

| Symbol                         | Parameter                     | Value      | Unit |

|--------------------------------|-------------------------------|------------|------|

| T <sub>A</sub>                 | Ambient Operating Temperature | 0 to 70    | °C   |

| T <sub>STG</sub>               | Storage Temperature           | -65 to 150 | °C   |

| V <sub>IO</sub> <sup>(2)</sup> | Input or Output Voltages      | –0.5 to 7  | V    |

| Vcc                            | Supply Voltage                | –0.5 to 7  | V    |

| lo <sup>(3)</sup>              | Output Current                | 20         | mA   |

| PD                             | Power Dissipation             | 1.2        | W    |

Table 2. Absolute Maximum Ratings (1)

Notes: 1. Except for the rating "Operating Temperature Range" stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents.

2. Up to a maximum operating Vcc of 5.5V only.

3. One output at a time, not to exceed 1 second duration.

#### **DESCRIPTION** (cont'd)

9 bits. It is fabricated using SGS-THOMSON's low power, high performance, CMOS technology. The device integrates a 2-bit burst counter, input registers, high output drive capability, and high speed synchronous SRAM onto a single chip. The synchronous design provides precise control using an external clock (K) input. The M62486R is specifically adapted to provide a burstable, high performance secondary cache for the i486<sup>®</sup> microprocessor. The M62486R is available in a 44 lead Plastic Leaded Chip Carrier package (PLCC). The device provides multiple power and ground pins to reduce effects induced by output noise for high performance applications. Separate power and ground pins (V<sub>CCQ</sub> and GND<sub>Q</sub>) have been employed for DQ0-DQ8 to allow output levels referenced to 5V or 3.3V. For proper operation all GND and GND<sub>Q</sub> pin must be connected to ground. V<sub>CC</sub>  $\geq$  V<sub>CCQ</sub> at all times including power-up.

The main Burst SRAM power requires a single 5V  $\pm$  5% supply, and all inputs and outputs are TTL compatible.

#### **DEVICE OPERATIONS**

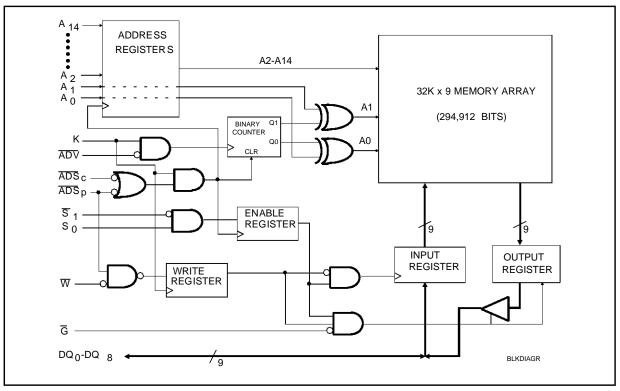

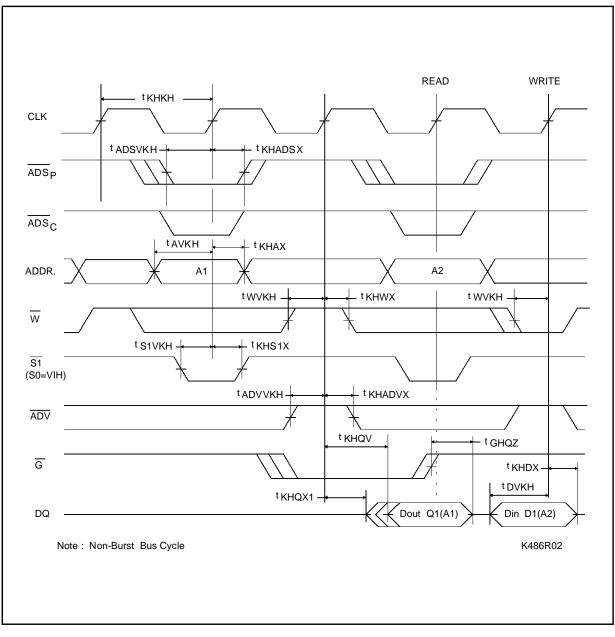

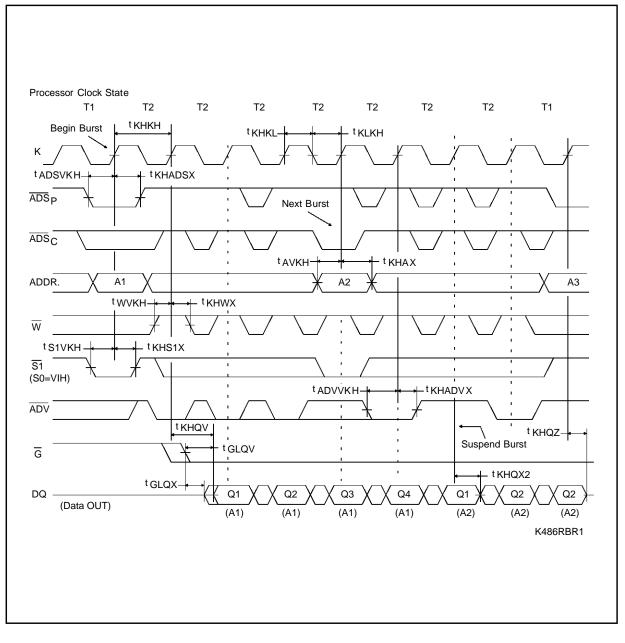

Addresses (A0-A14), data inputs (DQ0-DQ8), and control signals, with exception of Output Enable ( $\overline{G}$ ), are clock controlled inputs through non-inverting, pos-itive edge triggered registers. A cache burst address sequence can be initiated by either  $\overline{ADSP}$  (Address Status Processor) or  $\overline{ADSC}$  (Address Status Cache Controller) inputs, with subsequent burst addresses being <u>internally</u> generated by the Burst SRAM. The ADV input (burst address advance) provides control of the burst sequence, which imitates the i486 cache burst address sequence. Once a cache burst cycle begins, the subsequent burst address is generated internally each time the  $\overline{ADV}$  input is asserted at the rising edge of the clock (K) input.

#### Table 3. Asynchronous Truth Table

| Mode                 | G | DQ Status        |

|----------------------|---|------------------|

| Read                 | L | Data Out         |

| Read                 | Н | High-Z           |

| Write <sup>(2)</sup> | Х | Data In (High-Z) |

| Deselect             | Х | High-Z           |

Notes: 1. X = Don't Care.

For a cache write cycle following a read operation, G must be high before the input data required set-up time, and be held high through the input data hold time.

#### Table 4. Burst Count Sequence

| External Address  | A14-A2 | A1 | A0 |

|-------------------|--------|----|----|

| 1st Burst Address | A14-A2 | A1 | ĀŌ |

| 2nd Burst Address | A14-A2 | A1 | A0 |

| 3rd Burst Address | A14-A2 | A1 | A0 |

Note: The burst count sequence wraps around to the initial address after a full count is completed.

| Table 5. | Synchronous Truth Tab | le |

|----------|-----------------------|----|

|----------|-----------------------|----|

| S0 | S1 | ADSP | ADSC | ADV | W | к          | Address                         | Operation                                |

|----|----|------|------|-----|---|------------|---------------------------------|------------------------------------------|

| L  | Х  | L    | Х    | Х   | Х | ↑          | N/A                             | Deselected                               |

| Х  | Н  | Н    | L    | Х   | Х | $\uparrow$ | N/A                             | Deselected                               |

| н  | L  | L    | х    | х   | х | Ŷ          | External Base Address           | Read Cycle - Begin<br>Burst              |

| Н  | L  | Н    | L    | х   | L | Ŷ          | External Base Address           | Write Cycle - Begin<br>Burst             |

| Н  | L  | Н    | L    | х   | Н | Ŷ          | External Base Address           | Read Cycle - Begin<br>Burst              |

| х  | х  | Н    | Н    | L   | L | Ŷ          | Advance Burst Address           | Write Cycle - Continue<br>Burst Sequence |

| х  | х  | н    | н    | L   | н | Ŷ          | Advance Burst Address           | Read Cycle - Continue<br>Burst Sequence  |

| х  | х  | Н    | Н    | Н   | L | Ŷ          | Hold Current Burst<br>Address   | Write Cycle - Suspend<br>Burst Sequence  |

| х  | х  | Н    | Н    | Н   | н | Ŷ          | Hold Current Burst •<br>Address | Read Cycle - Suspend<br>Burst Sequence   |

Notes: 1. X = Don't Care.

2. All inputs except  $\overline{G}$  require set-up and hold times to the rising edge (low to high transition) of the external clock (K).

3. All read and write timings are referenced from  $\overline{G}$  or K.

4. A read cycle is defined by W high or ADSP low for the required set-up and hold times. A write cycle is defined by W being asserted low for the set-up and hold times.

5.  $\overline{G}$  is a don't care when  $\overline{W}$  is registered low from the previous rising clock edge

6. Chip Selects must be true (S0 = high, S1 = low) at each rising of the clock while ADSP or ADSC is asserted for the device to remain enabled; Chip Selects are registered whenever ADSP or ADSC is asserted low at the rising edge of the clock.

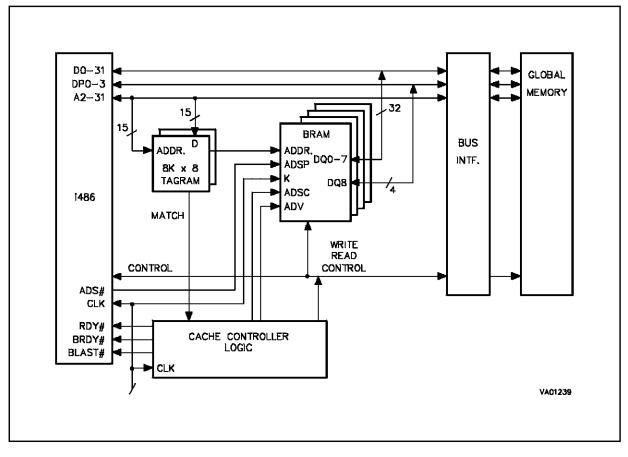

#### Figure 3. Block Diagram

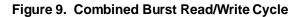

#### DEVICE OPERATIONS (cont'd)

The burst counter operates in the same manner for either cache burst write or read cycles. The ADSP and the ADSC inputs control the start and the duration of the burst sequence respectively. Each time either address status input is asserted low, a new external base address is registered on the positive going edge of the clock (K).

When ADSP is asserted low, any ongoing burst cycle is interrupted, and a read operation (independent of  $\overline{W}$  and  $\overline{ADSC}$ ) is performed at the new registered external base address. Anew burst cycle is initiated each time ADSP is asserted. By asserting ADSC low, the present burst cycle (initiated by ADSP) is interrupted and an extended burst read or write (depending upon the logic state of  $\overline{W}$  at the rising edge of K) is performed at the new registered base address. Chip selects (S0 and  $\overline{S1}$ ) are only sampled when a new base address is loaded. Therefore, the chip selects are registered when either address status input is asserted low at the rising edge of the clock (K), and remain latched internally until the next assertion of either ADSP or ADSC. The M62486R Truth Tables and timing diagrams reference specific device operations.

It should be noted that the M62486R allows a non-burst mode of operation where  $\overline{\text{ADSP}}$  is the ADS# of the i486 processor in a 2-2 cycle mode of

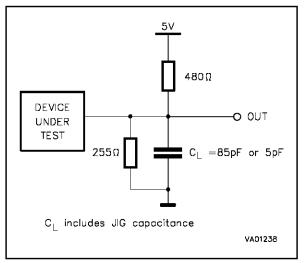

#### AC MEASUREMENT CONDITIONS

| Input Rise and Fall Times             | ≤ 1.5ns |

|---------------------------------------|---------|

| Input Pulse Voltages                  | 0 to 3V |

| Input and Output Timing Ref. Voltages | 1.5V    |

Note that Output Hi-Z is defined as the point where data is no longer driven.

#### Figure 4. AC Testing Load Circuit

## Table 6. Capacitance<sup>(1)</sup> (T<sub>A</sub> = 25 °C, f = 1 MHz )

| Symbol              | Parameter                                 | Test Condition        | Min | Мах | Unit |

|---------------------|-------------------------------------------|-----------------------|-----|-----|------|

| CIN                 | Input Capacitance on all pins (except DQ) | Vin = 0V              |     | 5   | pF   |

| Cout <sup>(2)</sup> | Output Capacitance                        | V <sub>OUT</sub> = 0V |     | 10  | pF   |

Notes: 1. Sampled only, not 100% tested 2. Outputs deselected

Table 7. DC Characteristics (T<sub>A</sub> = 0 to 70 °C, V<sub>CC</sub> = 5V  $\pm$  5%)

| Symbol                          | Parameter                        | Test Condition                                                                                                                                                  | Min  | Max                   | Unit |

|---------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|------|

| ILI                             | Input Leakage Current            | $0V \leq V_{IN} \leq V_{CC}$                                                                                                                                    |      | ±1                    | μA   |

| Ilo                             | Output Leakage Current           | $0V \le V_{OUT} \le V_{CC}$                                                                                                                                     |      | ±1                    | μA   |

| I <sub>CC1</sub> <sup>(1)</sup> | Supply Current                   | $\label{eq:G} \begin{split} \overline{G} &= V_{IH}, \ S0 = V_{IH}, \ \overline{S1} = V_{IL}, \\ All \ inputs = V_{IL} = 0V \\ and \ V_{IH} \geq 3V \end{split}$ |      | 180                   | mA   |

| Icc2 <sup>(2)</sup>             | Supply Current (Standby) TTL     | $S0 = V_{IL}, \overline{S1} = V_{IH}$                                                                                                                           |      | 40                    | mA   |

| I <sub>CC3</sub> <sup>(3)</sup> | Supply Current (Standby)<br>CMOS | $S0 \leq 0.2 \text{V},  \overline{S1} \geq \text{V}_{\text{CC}} - 0.2 \text{V}$                                                                                 |      | 30                    | mA   |

| VIL                             | Input Low Voltage                |                                                                                                                                                                 | -0.3 | 0.8                   | V    |

| VIH                             | Input High Voltage               |                                                                                                                                                                 | 2.2  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>                 | Output Low Voltage               | I <sub>OL</sub> = 8mA                                                                                                                                           |      | 0.4                   | V    |

| V <sub>OH</sub>                 | Output High Voltage              | I <sub>OH</sub> = –4mA                                                                                                                                          | 2.4  |                       | V    |

Notes: 1. Average AC current, Outputs open, cycling at  $t_{KHKH}$  minimum 2. All other Inputs at  $V_{IL} \leq 0.8V$  or  $V_{IH} \geq 2.2V$  3. All other Inputs at  $V_{IL} \leq 0.2V$  or  $V_{IH} \geq V_{CC} - 0.2V$

Figure 5. General 128K Byte Cache Block Diagram

#### DEVICE OPERATIONS (cont'd)

operation, and ADSC is held high during T2 (see Figure 5). However, the non-burst mode obviously negates the advantage of the internal burst counter for fast cache fill operations. In either mode (burst or non-burst), the write cycles are internally selftimed, and are initiated by the rising edge of the clock input. Self-timed write cycles eliminate complex off-chip write pulse generation providing more flexibility for incoming signals.

The  $\overline{\text{ADV}}$  input controls subsequent burst data accesses after the first data of the burst cycle is processed. Each time  $\overline{\text{ADV}}$  is asserted low for subsequent bursts at the rising edge of the clock input, the burst counter is advanced to the next

burst address sequence. The address is advanced before the operation. Wait states can be inserted during burst cycles by holding the ADV pin high during positive clock transitions. Upon completion of the full internal burst count, the address will wrap-around to its initial base address.

#### **GENERAL APPLICATION**

The M62486R is organized using the ninth bit as the parity bit to support byte parity. Since the i486 processor provides on-board parity generation and checking, the ninth bit of the cache Burst SRAM can be passed to one of the DP0-DP3 pins of the microprocessor. Thus the M62486R provides an architecture for building a 32K x 32bit burstable data cache SRAM array, with byte parity, by using four devices in a 128K byte cache application.

|                     |                                               |      | M62  | M62486R |      |      |      |  |

|---------------------|-----------------------------------------------|------|------|---------|------|------|------|--|

| Symbol              | Parameter                                     |      | 8    |         | 9    | Unit | Note |  |

|                     |                                               | Min. | Max. | Min.    | Max. |      |      |  |

| t <sub>кнкн</sub>   | Cycle Time                                    | 15   |      | 15      |      | ns   |      |  |

| tĸHQV               | Clock Access Time                             |      | 8    |         | 9    | ns   | 1    |  |

| t <sub>KHKL</sub>   | Clock High Pulse Width                        | 5.5  |      | 5.5     |      | ns   |      |  |

| t <sub>KLKH</sub>   | Clock Low Pulse Width                         | 5.5  |      | 5.5     |      | ns   |      |  |

| t <sub>GLQV</sub>   | Output Enable Access Time                     |      | 5    |         | 6    | ns   | 1    |  |

| t <sub>KHQX2</sub>  | Clock High to Output Hold Time                | 2    |      | 2       |      | ns   | 1    |  |

| t <sub>GLQX</sub>   | Output Enable to Output Active                | 0    |      | 0       |      | ns   | 2    |  |

| t <sub>KHQX1</sub>  | Clock High to Q Active (Low-Z)                | 3    |      | 3       |      | ns   | 2    |  |

| t <sub>KHQZ</sub>   | Clock High to Q High-Z                        |      | 6    |         | 6    | ns   | 2    |  |

| t <sub>GHQZ</sub>   | Output Disable to Q High-Z                    |      | 6    |         | 6    | ns   | 2    |  |

| t <sub>AVKH</sub>   | Address Set-up Time                           | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>ADSVKH</sub> | Address Status Set-up Time                    | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>DVKH</sub>   | Data In Set-up Time                           | 2    |      | 2       |      | ns   | 3    |  |

| tw∨кн               | Write/Read Set-up Time                        | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>ADVVKH</sub> | Address Advance Set-up Time                   | 2    |      | 2       |      | ns   | 3    |  |

| tsovкн              | Chip Select 0 (S0) Set-up Time                | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>S1VKH</sub>  | Chip Select 1 ( $\overline{S1}$ ) Set-up Time | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>KHAX</sub>   | Address Hold Time                             | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>KHADSX</sub> | Address Status Hold Time                      | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>KHDX</sub>   | Data In Hold Time                             | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>KHWX</sub>   | Write/Read Hold Time                          | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>KHADVX</sub> | Address Advance Hold Time                     | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>KHS0X</sub>  | Chip Select 0 (S0) Hold Time                  | 2    |      | 2       |      | ns   | 3    |  |

| t <sub>KHS1X</sub>  | Chip Select 1 ( $\overline{S1}$ ) Hold Time   | 2    |      | 2       |      | ns   | 3    |  |

#### Table 8. Read and Write Modes AC Characteristics ( $T_A = 0$ to 70°C, $V_{CC} = 5V \pm 5\%$ )

Notes: 1. C<sub>L</sub> = 85pF (see Figure 4).

2. Transition is measured ± 500 mV from steady-stage voltage with C<sub>L</sub> = 5pF (see Figure 4). This parameter is sampled and not 100 % tested.

3. This is a synchronous device requiring that all inputs must meet the specified set-up and hold times with stable logic levels for all rising edges of the clock input (K).

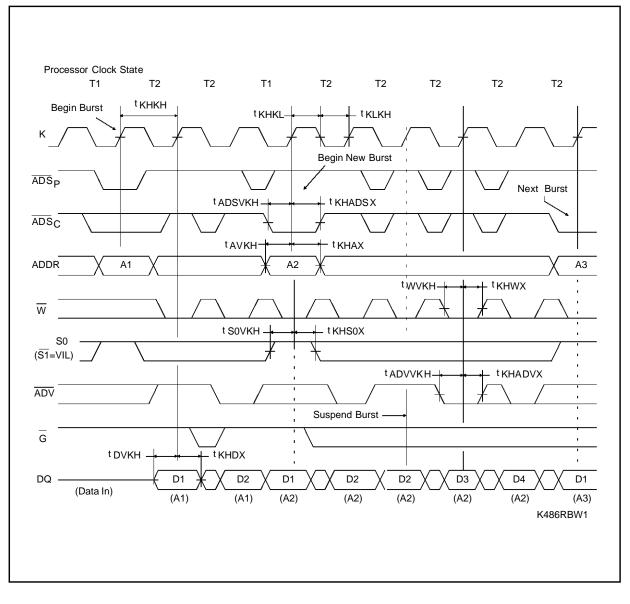

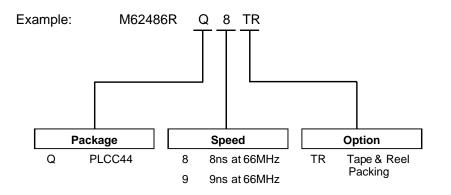

#### Figure 8. Burst Write Cycle

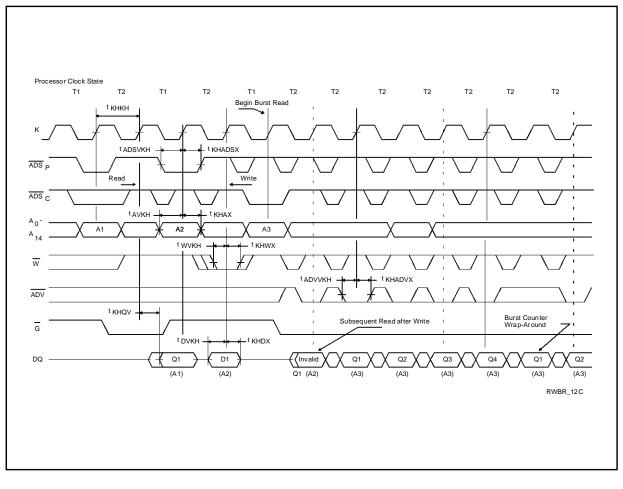

#### **ORDERING INFORMATION SCHEME**

For a list of available options (Package, Speed, etc...) refer to the current Memory Shortform catalogue. For further information on any aspect of this device, please contact SGS-THOMSON Sales Office nearest to you.

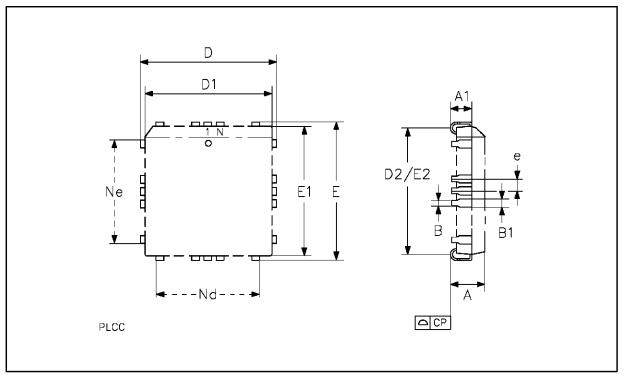

| Symb  |      | mm    |       |       | inches |       |  |

|-------|------|-------|-------|-------|--------|-------|--|

| Gynib | Тур  | Min   | Мах   | Тур   | o Min  |       |  |

| А     |      | 4.20  | 4.70  |       | 0.165  | 0.185 |  |

| A1    |      | 2.29  | 3.04  |       | 0.090  | 0.120 |  |

| В     |      | 0.33  | 0.53  |       | 0.013  | 0.021 |  |

| B1    |      | 0.66  | 0.81  |       | 0.026  | 0.032 |  |

| D     |      | 17.40 | 17.65 |       | 0.685  | 0.695 |  |

| D1    |      | 16.51 | 16.66 |       | 0.650  | 0.656 |  |

| D2    |      | 14.99 | 16.00 |       | 0.590  | 0.630 |  |

| E     |      | 17.40 | 17.65 |       | 0.685  | 0.695 |  |

| E1    |      | 16.51 | 16.66 |       | 0.650  | 0.656 |  |

| E2    |      | 14.99 | 16.00 |       | 0.590  | 0.630 |  |

| е     | 1.27 | _     | _     | 0.050 | _      | _     |  |

| Ν     |      | 44    |       | 44    |        |       |  |

| СР    |      |       | 0.10  |       |        | 0.004 |  |

## PLCC44 - 44 lead Plastic Leaded Chip Carrier, square

PLCC44

Drawing is out of scale

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics produds are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

<sup>™</sup> BRAM is a trademark of SGS-THOMSON Microelectronics

® i486 is a registered trademark of Intel Corporation

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malaysia - Malata - Morocco - The Netherlands -Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.